SoC设计项目:在FPGA上实现M0内核及视频图像处理

# 基础介绍

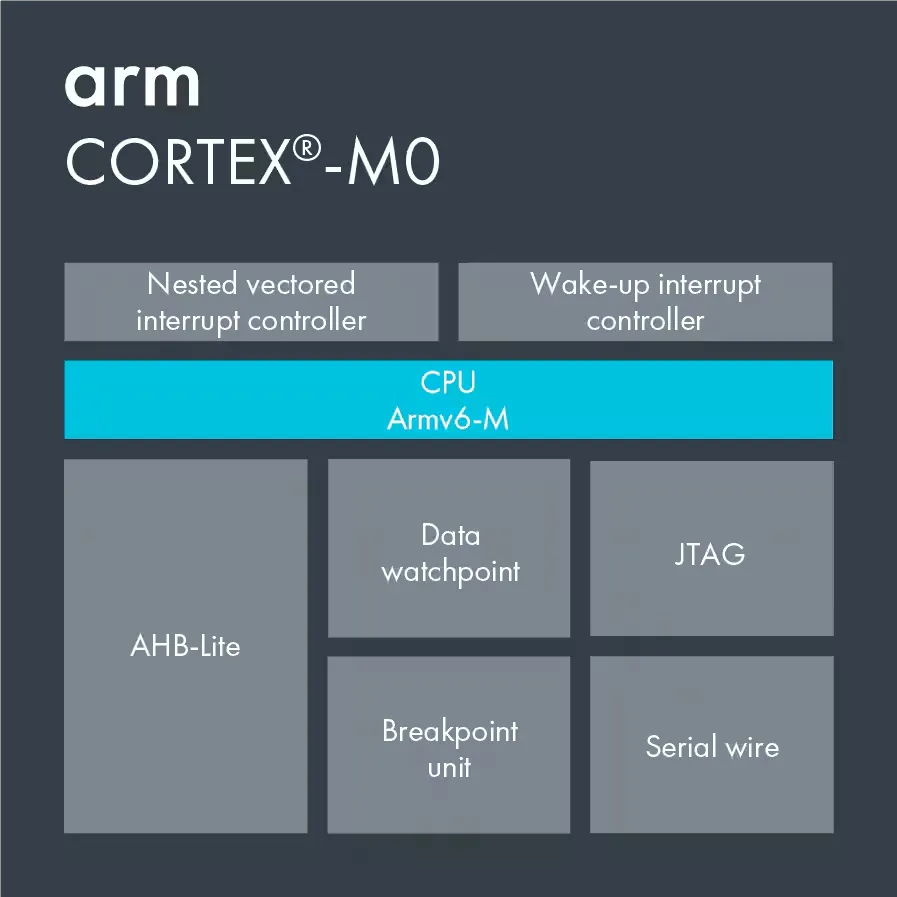

# Cortex-M0

Cortex-M0 是 ARM 公司在 2009 年发布的一款处理器,它基于冯・诺依曼架构,使用 32 位的精简指令集(RISC),Cortex-M0 的架构是 ARMv6-M,其中 M 表示的是架构的指令集为 Thumb 指令集的子集,虽然 ARM Cortex-M0 和 M0 + 两种微内核属于 ARMv6 版,但发布日期却在 ARMv7 之后,ARM 为了实现使用户能够在 FPGA 上使用 ARM 处理器以及实现超低功耗的嵌入式处理器应用,综合 ARMv7 的存储器系统和编程模型等技术,支持 Thumb-2 指令集 并针对功耗做进一步优化了现有的 ARMv6 架构,开发出了 ARMv6-M 架构,

下图是 Cortex-M0 的系统框图

包括

-

处理器核心

- 寄存器组

- 算术逻辑单元(ALU)

- 数据总线

- 控制逻辑

- 三级流线设计:取指、译码、执行

- 0.85~1.27 DMIPS/MHz

-

嵌套向量中断控制器 NVIC

-

32 个中断请求

-

1 个不可屏蔽中断输入(NMI)

-

-

内部总线系统

- 32 位总线

目前 ARM 已经开放了 M0 和 M3 的 IP 核,可在如下的链接下载,或者去官网下载中心搜索

关于 M0 内核的相关内容,以后再写一篇博客,这里就不多赘述

# AHB-Lite

AHB-Lite 是 AHB 的子集,是一个单主多从的总线,其结构框图如下,图中位 1 个 Master 和 3 个 Slave

AHB-Lite 的大致工作流程是,主机发送地址和数据,(事实上是分两个时钟发出的,数据滞后地址一个时钟周期),解码器通过对地址解码,为对应的从机及多路选择器提供选择信号,选中对应的从机进行通信

- 当主机写入时,根据 HSEL 信号,被选中的从机此时可以读取总线上的数据信号 HWDATA,更新自己的寄存器

- 当主机读取时,Slave 产生自己的 HRDATA_x 信号,多路选择器会根据解码器提供的选择信号,选择对应从机的 HRDATA_x 映射到 HRDATA 上

更多详细内容可以参考官方的数据手册:AMBA 3 AHB-Lite Protocol Specification (umich.edu)

# FPGA

看这个博客的应该不需要 FPGA 的介绍,如果不清楚可以去搜一下先补补课,本次项目使用的 FPGA 为安路科技的 EG4S20BG256,它的主要资源如下

- 逻辑资源:19600 LUTs

- 片内存储资源:

- 64 块 9Kb 嵌入式 RAM (ERAM9K)、16 块 32Kb 嵌入式 RAM

- 64Mb 内置 SDRAM(2M*32bits)

- 最大 156.8Kb 分布式 RAM

- 时钟资源

- 16 个全局时钟

- 4 个 PLL

本次做视频图像显示,主要考虑存储、时钟和布线资源

首先是存储,这个芯片内置了一块 SDRAM 就方便了许多,要想缓存一帧 1080P 图像至少需要 16Mbits(2MB)的空间,而要想增加乒乓操作则需要再加一倍,如果没有的话可能就外挂一块 SDRAM

时钟上 HDMI 1080P@60Hz 需要 148.5MHz 的像素时钟和 742.5MHz 的像素时钟 x5,因此需要满足可输出的最大时钟要不小于 742.5MHz,这个芯片的 PLL 最大可输出 750MHz,因此也满足

此外这个芯片支持最高 800Mbps 的 True LVDS,选择特定的引脚在布线时会自动生成 LVDS 通道,相比于之前用 Xilinx 的 FPGA 做 HDMI 输出使用原语实现 LVDS 就少了一步,还挺方便的,并且也满足 HDMI 1080P@60Hz 的要求

# ISP

ISP, Image Signal Process,即图像信号处理,目前有很多成熟的 ISP 算法,比如色域转换、去噪、白平衡、gamma 矫正、滤波等处理,最常见的应用就是相机

# ARM 软核移植

首先是软核移植

# ISP 算法设计

这些算法目前使用高级语言可以很轻松的实现,但是在 FPGA 上部署需要复杂一些,主要问题是缓存和时序,比如对很多算法来说需要进行算子运算,而算子运算则需要,对原有的图像数据